| Revision as of 23:24, 4 May 2008 editDavidPaulHamilton (talk | contribs)237 edits then you disambiguate and do not add unknown units← Previous edit | Revision as of 23:58, 4 May 2008 edit undoFnagaton (talk | contribs)3,957 edits Whoops x 2Next edit → | ||

| (2 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

| In ], '''Physical Address Extension''' ('''PAE''') refers to a feature of ] and ] processors that allows more than 4 ]s (]) of ] to be used in ] systems, given appropriate ] support |

In ], '''Physical Address Extension''' ('''PAE''') refers to a feature of ] and ] processors that allows more than 4 ]s (]) of ] to be used in ] systems, given appropriate ] support<ref>1 GB = 1024 ]</ref> PAE is provided by ] ] and above ] (including all later Pentium-series processors except the 400 MHz bus versions of the ]), as well as by some compatible processors such as ] and later models from ]. | ||

| The x86 processor hardware is augmented with additional address lines used to select the additional memory, so physical address size is increased from 32 bits to 36 bits. This increases maximum physical memory size from 4 GB to 64 GB. | The x86 processor hardware is augmented with additional address lines used to select the additional memory, so physical address size is increased from 32 bits to 36 bits. This increases maximum physical memory size from 4 GB to 64 GB. | ||

| Line 8: | Line 8: | ||

| ==Page table structures== | ==Page table structures== | ||

| In traditional 32-bit ], x86 processors use a two-level page translation scheme, where the ] <code>CR3</code> points to a single 4 KB long ''page directory'', which is divided into 1024 x 4 byte entries that point to 4 KB long ]s, similarly consisting of 1024 x 4 byte entries pointing to 4 KB long ]. | In traditional 32-bit ], x86 processors use a two-level page translation scheme, where the ] <code>CR3</code> points to a single 4 KB long ''page directory'', which is divided into 1024 x 4 byte entries that point to 4 KB long ]s, similarly consisting of 1024 x 4 byte entries pointing to 4 KB long ].<ref>As mentioned in the article text it is unambiguous in this context that 1 KB = 1024 ]</ref> | ||

| Enabling PAE (by setting bit 5, ''PAE'', of the system register <code>CR4</code>) causes major changes to this scheme. By default, the size of each page remains as 4 KB. Each entry in the page table and page directory is extended to 64 bits (8 bytes) rather than 32 bits to allow for additional address bits; however, the size of tables ''does not'' change, so both table and directory now have only 512 entries. Because this allows only half as many entries as the original scheme, an extra level of hierarchy has been added, so CR3 now points to the ''Page Directory Pointer Table'', a short table which contains pointers to 4 page directories. | Enabling PAE (by setting bit 5, ''PAE'', of the system register <code>CR4</code>) causes major changes to this scheme. By default, the size of each page remains as 4 KB. Each entry in the page table and page directory is extended to 64 bits (8 bytes) rather than 32 bits to allow for additional address bits; however, the size of tables ''does not'' change, so both table and directory now have only 512 entries. Because this allows only half as many entries as the original scheme, an extra level of hierarchy has been added, so CR3 now points to the ''Page Directory Pointer Table'', a short table which contains pointers to 4 page directories. | ||

| The entries in the page directory have an additional flag, in bit 7, named <code>PS</code> (for ''Page Size''). If this bit is set to 1, the page directory entry does not point to a page table, but to a single large 2 MB page. The ] is another flag in the page directory, in bit 63, to mark pages as "No eXecute". Because the 12 most significant bits of page table entry's 64 bits are either such flags or are available for OS-specific data, a maximum of 52 bits can be potentially utilized in future to address 2<sup>52</sup> bytes, or 4 ]s, of physical memory. | The entries in the page directory have an additional flag, in bit 7, named <code>PS</code> (for ''Page Size''). If this bit is set to 1, the page directory entry does not point to a page table, but to a single large 2 MB page.<ref>1 MB = 1024 ]</ref> The ] is another flag in the page directory, in bit 63, to mark pages as "No eXecute". Because the 12 most significant bits of page table entry's 64 bits are either such flags or are available for OS-specific data, a maximum of 52 bits can be potentially utilized in future to address 2<sup>52</sup> bytes, or 4 ]s, of physical memory.<ref>As mentioned in the article text it is unambiguous in this context that 1 PB = 2<sup>50</sup> ]</ref> | ||

| The ] presently uses only 36 bits out of 52 bits possible. On ] processors, PAE is obligatory in native ]; presently 40 bits are used out of 52 bits possible.<ref>{{cite web | The ] presently uses only 36 bits out of 52 bits possible. On ] processors, PAE is obligatory in native ]; presently 40 bits are used out of 52 bits possible.<ref>{{cite web | ||

Revision as of 23:58, 4 May 2008

In computing, Physical Address Extension (PAE) refers to a feature of x86 and x86-64 processors that allows more than 4 gigabytes (GB) of physical memory to be used in 32-bit systems, given appropriate operating system support PAE is provided by Intel Pentium Pro and above CPUs (including all later Pentium-series processors except the 400 MHz bus versions of the Pentium M), as well as by some compatible processors such as Athlon and later models from AMD.

The x86 processor hardware is augmented with additional address lines used to select the additional memory, so physical address size is increased from 32 bits to 36 bits. This increases maximum physical memory size from 4 GB to 64 GB. The 32-bit size of virtual address is not changed, so regular application software continues to use instructions with 32-bit addresses and (in a flat memory model) is limited to 4 gigabytes (GB). The operating system uses page tables to map this 4 GB address space onto the 64 GB of total memory, and the map is usually different for each process. In this way the extra memory is useful even though no single regular application can access it all simultaneously.

For application software which needs access to more than 4 GB of memory, some special mechanism may be provided by the operating system in addition to the regular PAE support. On Microsoft Windows this mechanism is called Address Windowing Extensions (AWE), while on Unix-like systems a variety of tricks are used, such as using mmap() to map regions of a file into and out of the address space as needed, none having been blessed as a standard.

Page table structures

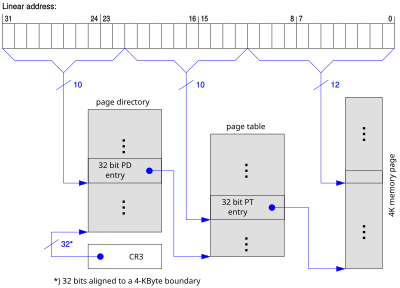

In traditional 32-bit protected mode, x86 processors use a two-level page translation scheme, where the control register CR3 points to a single 4 KB long page directory, which is divided into 1024 x 4 byte entries that point to 4 KB long page tables, similarly consisting of 1024 x 4 byte entries pointing to 4 KB long pages.

Enabling PAE (by setting bit 5, PAE, of the system register CR4) causes major changes to this scheme. By default, the size of each page remains as 4 KB. Each entry in the page table and page directory is extended to 64 bits (8 bytes) rather than 32 bits to allow for additional address bits; however, the size of tables does not change, so both table and directory now have only 512 entries. Because this allows only half as many entries as the original scheme, an extra level of hierarchy has been added, so CR3 now points to the Page Directory Pointer Table, a short table which contains pointers to 4 page directories.

The entries in the page directory have an additional flag, in bit 7, named PS (for Page Size). If this bit is set to 1, the page directory entry does not point to a page table, but to a single large 2 MB page. The NX bit is another flag in the page directory, in bit 63, to mark pages as "No eXecute". Because the 12 most significant bits of page table entry's 64 bits are either such flags or are available for OS-specific data, a maximum of 52 bits can be potentially utilized in future to address 2 bytes, or 4 petabytes, of physical memory.

The x86 architecture presently uses only 36 bits out of 52 bits possible. On x86-64 processors, PAE is obligatory in native long mode; presently 40 bits are used out of 52 bits possible.

CPU support of PAE mode can be identified via the CPUID flag PAE.

Operating system support

FreeBSD

FreeBSD supports PAE in the 4.x series starting with 4.9, in the 5.x series starting with 5.1, and in all 6.x and later releases. The kernel PAE configuration option is required. Loadable kernel modules can only be loaded into a kernel with PAE enabled if the modules were built with PAE enabled; the binary modules in FreeBSD distributions are not built with PAE enabled, and thus cannot be loaded into PAE kernels. Not all drivers support more than 4 GB of physical memory; those drivers won't work correctly on a system with PAE.

Linux

The Linux kernel includes full PAE support starting with version 2.6. The 2.6 version of the kernel fully supports PAE, enabling access of up to 64 GB of memory on 32-bit machines. A PAE-enabled Linux-kernel requires that the CPU also support PAE.

Solaris

Solaris supports PAE beginning with Solaris version 7. However, third-party drivers used with version 7 and not specifically written to include PAE support may operate erratically or fail outright on a system with PAE.

Windows

PAE is supported in the following versions of 32-bit Windows:

Version Maximum Physical Memory Windows 2000 Advanced Server 8 GB Windows 2000 Datacenter Server 32 GB Windows XP 4 GB Windows Server 2003 Enterprise Edition 32 GB Windows Server 2003 R2 (or SP1) Enterprise Edition 64 GB Windows Server 2003 Datacenter Edition 64 GB Windows Server 2003 Standard Edition 4 GB Windows Vista 4 GB Windows Server 2008 Enterprise or Datacenter Edition 64 GB Windows Server 2008 other editions 4 GB

Windows XP SP2 and later by default on processors with the no-execute (NX) or execute-disable (XD) feature runs in PAE mode in order to allow NX. The NX (or XD) bit resides in bit 63 of the page table entry, and without PAE, page table entries only have 32 bits; therefore PAE mode is required if the NX feature is to be exploited. However, desktop versions of Windows (Windows XP, Windows Vista) limit physical address space to 4 GB for driver compatibility reasons.

See also

- PSE-36: an alternative to Physical Address Extension

- Page Size Extension

- Architecture of Windows NT

References

- 1 GB = 1024 MB

- As mentioned in the article text it is unambiguous in this context that 1 KB = 1024 B

- 1 MB = 1024 KB

- As mentioned in the article text it is unambiguous in this context that 1 PB = 2 B

- "Intel 64 and IA-32 Software Developer's Manual - Volume 3A" (PDF). Intel. Retrieved 2007-11-16. Page 3.42.

- "FreeBSD PAE(4) man page". 2003-04-08. Retrieved 2007-11-26.

- "Wonderful World of Linux 2.6".

- "Solaris 7 5/99 Release Notes (Intel Platform Edition), Appendix B: Hardware Compatibility List and Device Configuration Guide (Intel Platform Edition) 5/99". 1999. Retrieved 2007-11-26.

- "Memory Limits for Windows releases". Microsoft. December 5, 2007. Retrieved 2007-12-10.

- "Intel Physical Addressing Extensions (PAE) in Windows 2000". Microsoft. October 26, 2007. Retrieved 2007-12-29.

- "Physical Address Extension". Microsoft.

- "Memory Support and Windows Operating Systems". 2007. Retrieved 2008-03-22.

External links

- Windows PAE entry on MSDN Library

- Windows PAE entry on Microsoft knowledge base

- Paging Extensions for the Pentium Pro Processor